先进封装:TSMC在FOPLP和CoPoS方面的战略推动

先进封装被广泛认为是扩展和超越摩尔定律的关键技术途径。面对芯片扩展的物理限制和工艺节点小型化步伐的放缓,先进封装通过系统级封装 (SiP)、异构集成和高密度互连实现计算性能和能效的持续改进。

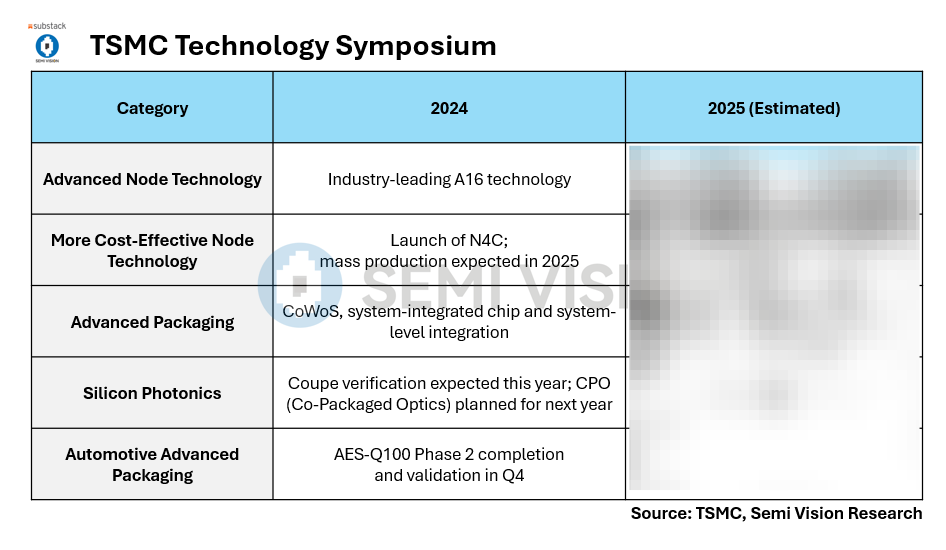

台积电的技术论坛即将举行,据外媒报道,预计台积电将在活动中讨论 CoPoS 的技术概念。这将与 2025 Touch Taiwan 技术论坛同时进行,产生协同效应。SemiVision Research 将对 CoPoS 技术进行深入讨论,并分析台湾和全球供应链格局。

由于这种封装技术与基于面板的工艺密切相关,台湾面板制造商群创光电已成为讨论中的领先公司。然而,他们的主要关注点一直是 FOPLP(扇出面板级封装)而不是 CoPoS。

FOPLP(扇出面板级封装)和 CoPoS(Chip-on-Panel-on-Substrate)都使用大型面板基板进行封装,但它们在架构和应用方面存在显著差异,尤其是在中介层的使用方面。FOPLP 是一种没有中介层的封装方法,其中芯片芯片直接重新分配到面板基板上,并通过再分配层 (RDL) 互连。这带来了成本更低、I/O 密度高和外形尺寸灵活的等优势,使其适用于集成密度适中的边缘 AI、移动设备和中端 ASIC 等应用。

相比之下,CoPoS 集成了中介层,可实现更高的信号完整性和稳定的功率传输,这在集成多个高性能、高功率芯片(如 GPU 和 HBM)时尤为重要。中介层的存在使 CoPoS 更适合需要大面积封装和高速数据传输的高端 AI 和 HPC 系统。

此外,CoPoS 中的中介层材料正在从传统的硅发展为玻璃,这提供了更好的成本效益和热稳定性。玻璃中介层还提供改进的热膨胀系数 (CTE) 匹配和减少翘曲,从而提高产量和更好的大面积集成工艺控制。这是台积电及其供应链合作伙伴的重点,将 CoPoS 定位为未来 CoWoS-L 的潜在替代品。

之前,我们深入讨论了为什么先进封装是必不可少的,并分析了台积电对 Chip-on-Panel-on-Substrate (CoPoS) 的战略推广。这种方法响应了不断增长的 AI GPU 封装面积需求和 CoWoS 的产能限制,基于面板的基板成为未来扩展和成本优化的关键推动因素。

现在,我们将重点转向TSMC在扇出面板级封装 (FOPLP) 和更广泛的 CoPoS 生态系统方面的现状。

新兴的 FOPLP 和 CoPoS 技术推动测试和分析行业

由于人工智能技术需要更快的处理速度和更低的功耗,台积电 一直在积极投资先进封装和硅光子学。这一战略举措刺激了测试和分析领域的需求增加,行业专家乐观地认为,CoPoS、FOPLP(扇出面板级封装)和硅光子学等发展将继续推动这一需求,从而加强 HKC、爱德万测试和宜特等测试公司的运营。

CoPoS 是一种简化从晶圆到面板形式的过渡的技术,类似于 CoWoS 的面板化,并利用方形基板来集成更多芯片,从而提高生产效率和成本效益。但是,高温翘曲问题需要通过广泛的测试和分析来解决。

此外,据报道,台积电的第一代硅光子学产品,紧凑型通用光子引擎 (COUPE) 已进入验证阶段,并计划与共封装光学器件 (CPO) 模块一起进一步开发。这些技术需要额外的测试来支持最初的行业增长阶段。

爱德万测试最近在中国台湾和日本获得了硅光子光损耗检测设备的专利。这些器件可以识别半导体光导芯片路径中的异常情况,例如衰减、泄漏和断开,为解决光子集成电路 (PIC) 中普遍存在的问题铺平了道路,并利用了硅光子学市场的潜力。

爱德万测试去年的巨额资本支出最初抑制了利润,但对今年硅光子学和先进工艺技术收获阶段的预期表明运营和盈利能力有所改善。

宜特持续强化核心技术与客户服务,聚焦五大关键领域的先进制程与包装。这包括强调 CPO、TGV(穿玻璃通孔衬底)和 TSV(通硅通孔)解决方案,预计今年的收入和利润将出现双增长。

香港通讯还努力培育先进的流程,对中国台湾和日本市场的稳定增长前景持乐观态度。随着他们最近在今年第一季度的北海道实验室落成,材料分析业务连续性和产品组合优化应该会提高未来的盈利能力。

关键见解表

| 方面 | 描述 |

|---|---|

| CoPoS 技术 | 提高了芯片集成度和效率,但由于翘曲问题需要测试。 |

| 硅光子学 | 台积电正在开发的开创性 COUPE 产品,促进行业合作。 |